RISC-V, RISC-V, RISC-V – London

The BCS OSSG and the OSHUG are hosting their next event on 23rd November 2017, 18:00 – 21:00 at BCS London, 1st Floor, The Davidson Building, 5 Southampton Street, London, WC2E 7HA, [map] (51.510812, -0.121733)

The BCS OSSG and the OSHUG are hosting their next event on 23rd November 2017, 18:00 – 21:00 at BCS London, 1st Floor, The Davidson Building, 5 Southampton Street, London, WC2E 7HA, [map] (51.510812, -0.121733)

The event will be on the theme of RISC-V, an open ISA which started life at the University of California, Berkeley.

This event is free to attend for both BCS Members and non-members but booking is required. Places are limited; please book as soon as possible.

Bringing up cycle-accurate models of RISC-V cores

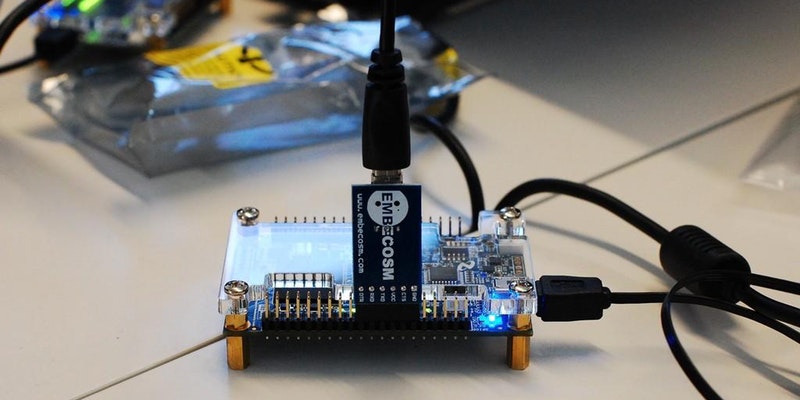

The openness of the RISC-V ISA has enabled the development of many open-source RISC-V cores with varying capabilities. Choosing an implementation that meets given requirements can be done to some extent by comparing specifications and other attributes of the cores, but any decision must be based on actual testing. Using Verilator to generate cycle-accurate models enables rapid development of testing platforms. This talk provides a report of our experience bringing up cycle-accurate models of two cores in particular, RI5CY from the PuLP project, and Clifford Wolf’s PicoRV32. For testing, a software ecosystem consisting of a compiler, binary utilities, debugger, and an interface between the model and debugger accompanies the Verilator model. To compare the cores, we used the GCC test suite and the RISC-V ISA test suite for measuring correctness, and the Bristol/Embecosm Embedded Benchmark Suite (BEEBS) to compare performance. All code and scripts used for the implementation are open-source, and can be re-used by others who wish to do similar exercises with other RISC-V cores.

Edward Jones has a background in parsing techniques and works at Embecosm on LLVM and GNU toolchains. He is also involved in research by Embecosm to investigate ways in which the software tool chain can reduce program energy consumption. Edward Jones is a Computer Science graduate of the University of Kent.

FreeBSD/RISC-V and Device Drivers

The FreeBSD port to RISC-V 64-bit ISA was added in January 2016. FreeBSD is the first operating system that officially supported RISC-V in the main repository. Since its introduction, support has evolved, RISC-V privileged architecture has updated a few times. The platform is maturing making it suitable for general, commercial, research and educational use. The GCC v7.0 target for RISC-V was officialy upstreamed and NVIDIA is planning to ship all of their GPUs with RISC-V coprocessor enabled in the future. Several companies have announced the start of RISC-V chip development and many universities are taking RISC-V as a target architecture for doing research. The world first RISC-V microcontroller-class board HiFive1 was released and we are getting closer to the first general purpose board to become available! This talk will describe the current status of FreeBSD/RISC-V, toolchain and supported simulators. The porting process as well as describing the latest changes made to FreeBSD in order to support the latest RISC-V privilege specification (v1.10). This includes enabling by default FDT support and drivers attachment change, SBI interface, compiler flags/built-in definition changes, support for updated BBL boot loader, RISC-V privilege levels, initial page tables build, page table entry flags and other changes. An overview of FreeBSD device drivers subsystem will also be covered describing the device frameworks, buses and kernel-interfaces that exists in FreeBSD (e.g. Newbus, cdevsw, bus_dma, SYSINIT, vt, sound, ifnet, spibus, etc), how to use and configure them and how to debug a device driver. This should answer the question: How to write device driver for FreeBSD/RISC-V?

Ruslan Bukin is a Research Associate at University of Cambridge Computer Laboratory. He has been a FreeBSD user since 2002 and src committer since 2013. His main interests and contributions to FreeBSD are related to computer architectures support, performance monitoring technologies support, hardware tracing technologies (Intel PT), devicedrivers, DMA engines and DMA frameworks, hardware security (Intel SGX, CHERI), heterogeneous computing. Ruslan is the lead developer of the FreeBSD/RISC-V project. He obtained a Computer Science degree in 2008 from Peoples’ Friendship University of Russia in Moscow

Talk #3 TBA

Note: Please aim to arrive by 18:15 as the event will start at 18:30 prompt.

Closing date for bookings is Tuesday 21st November 2017 at 11:30 pm. No more bookings will be taken after this date. For overseas delegates who wish to attend the event please note that BCS does not issue invitation letters

Since the workshops held earlier this year, numerous changes have been made to the NetBSD operating system to ensure future workshops are easier for users and work smoother from the outset. This talk will cover some of the improvements made so far and what’s currently in the works. From wrestling with the u-boot firmware to new tools included in the os and much more.

Since the workshops held earlier this year, numerous changes have been made to the NetBSD operating system to ensure future workshops are easier for users and work smoother from the outset. This talk will cover some of the improvements made so far and what’s currently in the works. From wrestling with the u-boot firmware to new tools included in the os and much more. ChipHack is an occasional 2 day workshop introducing students and hobbyists to FPGA design. This year, ChipHack was sponsored by the BCS OSSG and Computer Conservation Society. To celebrate the 60th anniversary of the BCS, the workshop was extended by half a day and attempted to reimagine one of the earliest valve computers, EDSAC, designed by the BCS’ founding president, Prof Sir Maurice Wilkes.

ChipHack is an occasional 2 day workshop introducing students and hobbyists to FPGA design. This year, ChipHack was sponsored by the BCS OSSG and Computer Conservation Society. To celebrate the 60th anniversary of the BCS, the workshop was extended by half a day and attempted to reimagine one of the earliest valve computers, EDSAC, designed by the BCS’ founding president, Prof Sir Maurice Wilkes.