30th June 2018, 09:00 Saturday morning – 16:00 on the Sunday afternoon at The Blue Room, The Lawn, Union Rd, Lincoln, LN1 3BU, [map].

Open Source Hardware Camp 2018 will be hosted in the historic county town of Lincoln — home to, amongst others, noted engine builders Ruston & Hornsby (now Siemens, via GEC and English Electric). This year OSHCamp will feature a total of 10 talks on the Saturday, with 7 hands-on workshops on the Sunday.

Lincoln is well served by rail, reachable from Leeds and London within 2-2.5 hours, and 4-5 hours from Edinburgh and Southampton.

There will be a social at the Wig and Mitre on the Saturday evening.

Tickets are priced at £10/day and this includes lunch.

To register visit: http://oshcamp2018.eventbrite.co.uk

Saturday :: Talks

Introduction to cycle-accurate Verilog simulation

Developing hardware designs in Verilog is tricky, for both FPGA platforms and ASIC hardware targets. Understanding the behaviour of a design, testing it, and debugging are made much easier by simulating in software. There are a variety of simulation approaches with different trade-offs in what properties of the design are accurately modelled and how quickly they run. This talk starts by giving a brief overview of the approaches, then focusing in more detail on cycle-accurate modelling, which is a relatively fast approach that is robustly implemented in an open-source tool called Verilator. The main focus will be on working with CPU designs, but the software and techniques are generally applicable to other areas.

A brief overview of how to use Verilator to simulate a design, to develop testbenches, and to visualise simulation output using GTKWave will be given. The software and techniques discussed in this talk will be put into practice in the “Open-source RISC-V core quickstart” workshop on Sunday.

Dr Graham Markall has a background in languages and compilers for scientific computing, and is well known for his work on the Numba project. He is part of Embecosm’s GNU tool chain team, where his current projects include the implementation of security enhancements to the GCC and LLVM compilers for RISC-V and ARM, and the development a GCC-based toolchain for a customised RISC-V processor.

LoRaWAN at 100,000 feet & 10mW with High Altitude Ballooning

High-altitude balloons are manned or unmanned balloons, usually filled with helium, that are released into the stratosphere and generally attaining between 18,000 to 37,000 metres (59,000 to 121,000 ft; 11 to 23 mi). In 2002, a balloon named BU60-1 attained 53.0 km (32.9 mi; 173,900 ft).

The advent of cheap open source electronics & suitable GPS chips has allowed hobbyists worldwide to build fly & (usually) recover these balloons since the mid 2000’s with modest budgets compared to professional weather balloons. Indeed, the Raspberry Pi Foundation ran a few Skycademy events aimed at helping school teachers. There is a wealth of information available from the United Kingdom High Altitude Society (UKHAS), their website HabHUB.org and Dave Ackerman’s website.

Ofcom limit the power of any airborne transmitter to 10mW, which whilst tiny isn’t a practical problem since the line of sight is usually superb. The community stated using RTTY initially but latterly has begun to use LoRaWAN to transmit the telemetry and some of the pictures taken during a typical 2 to 3 hour flight. The Civil Aviation Authority will grant permission for such flight via their system, NOTAMs. It’s normal to be asked to contact air traffic control before launch to make sure commercial aviation traffic isn’t hindered.

Tony Brookes is a member of the Derby Makers who is leading a project to launch such a balloon (or more if funding permits) over the summer. Derby Makers are now resident in the Radio Communications Museum of Great Britain in Derby following their tenure in the Derby Silk Mill museum which is now undergoing HLF funded refurbishment.

Machine Vision

Machine Vision is one of the fastest growing disciplines in robotics and automation. In the past, discrete vision processing tasks have been both complex and brittle requiring a great deal of specialisation and practice. Now however machine learning (ML) inference is becoming practical at the edge, Machine Vision is one of the emerging ‘edge applications’ of ML inference technology. Machine Vision is much less brittle than earlier approaches and promises much wider and simpler applications. This talk (and hands on workshop) will explore the landscape of Machine Vision and its applications for robotics and automation.

Alan Wood has been working with parallel distributed programming for several decades. His recent work includes smart grids, 3D printers, robotics, automation and biotec diagnostics. His current research is focused on machine learning for embedded automation using FPGA, CSP and Neural Turing Machines. He is a long term advocate of open source communities, a moderator (aka Folknology) for xCORE, the co-founder of myStorm open hardware FPGA community, as well as a co-founder of Surrey and Hampshire Makerspace.

Making Electronic Tesla Coils – Keeping in the Magic Smoke

This talk will give an overview of designing and building an electronic Tesla coil from off the shelf or easily modified components. It will cover the safety, construction methods and some of the theory of operation. It will also present details of the controls and methods needed to prevent the Tesla coil from destroying itself when power is applied.

Derek Woodroffe has been building Tesla coils as a hobby for over 20 years. He has constructed over 30 different Tesla coils, from 30mm to over 1M tall and of many different types. He runs both the Nottingham Gaussfest and Cambridge Tesla coiler meet-ups and has worked a number of times on TV to assist with Tesla coil and high voltage demonstrations to programs such as the Royal Institute Christmas Lectures and Dara O Briain’s Science club. Derek also has a keen interest in all other uses and generators of high voltage and has built working examples of many. His projects are detailed on www.extremeelectronics.co.uk.

Amazingly, he is still alive.

Turning your hobby project in to a business for fun and profit

Designing hardware is the easy part. Turning it in to a business is where it gets interesting. This talk will cover some of the things needed to take it to market, including stock, marketing, shipping, support, cash flow.

Spencer Owen like many kids in the 80s, loved his ZX Spectrum and other 8 bit computers. This set him up for a career in IT, and he worked as a server engineer and network engineer for many years. In 2013, in a bid to see if he really understood how computers worked at the lowest level, Spencer went back to his roots built a simple Z80 based machine on a breadboard. This was to mature in to the RC2014, which Spencer started selling in his spare time in 2015. Within a few months it was clear that the RC2014 was taking up more time than he had spare, so he quit network job and started a retro computer kit company. Spencer is now the largest supplier of Z80 computers worldwide.

MakerNet Alliance

A brief presentation of ideas the MakerNet Alliance is working on with E-nable.org for a Design Ecology Interface, to visualize the evolution of open source designs for prosthetics (and ultimately any hardware designs) and help users find the design version with the features they need. The presentation will be followed by discussion session with the audience to get feedback on the ideas and input on requirements.

Anna Sera Lowe has always been fascinated by how things are made and how they get to the people who need them. As a manufacturing manager and later a supply chain consultant, she made a career of finding great excuses to visit manufacturing facilities around the globe; from multi-million dollar automated factories to informal waste-processing operations on dumps (sometimes next to each other) – and everything in between. She has consulted for clients as diverse as Johnson & Johnson, the state electricity monopoly of South Africa, and the Global Fund to Fight Aids, Tuberculosis, and Malaria. Over the last few years her interest has been caught by ideas around grassroots innovation and distributed manufacturing networks. She co-founded Kumasi Hive, a makerspace in Ghana, and is leading work on MakerNet, an initiative to explore business models and digital tools for local manufacturing of useful goods for development.

EMC for IoT

Often the last thing on your mind when working on an exciting new project are the regulatory hurdles that come with getting a product ready for sale in the European market. These afterthoughts suddenly become pressing priorities as you approach your launch date. Electro-Magnetic Compatibility (EMC) is the study of how all electronic devices and phenomena interact and, in our increasingly electro-dense society, these requirements become all the more important. Without EMC and radio regulations we would suffer interference to the wireless infrastructure we so depend on.

This talk will give a tour through the EMC and radio regulations for a typical IoT type product (equally applicable to any electronics product), why they are required and look at some of the risks and pitfalls involved in the process. If you’ve got a product that you want to start selling, have limited experience or are merely EMC-curious then this talk will be extremely useful. Questions often asked include: Why do I need to do EMC testing? What about if I have a radio module in my product? What sort of certificate should I have? Do I even need to do anything? You’ll find some of the answers here.

James Pawson, Unit 3 Compliance. Having a broad background of electronics experience (and also a beard), James found himself drawn to the field of EMC partly because of the interesting variety of work and partly because no one else wanted to do it. Twelve years later, now with his own test laboratory and consultancy business, he has found his vocation in helping solve people’s EMC problems. He’s also found more grey hairs in his beard and worries that the two are related.

Non-Standard Computation — From Bits to Pulses to Spikes

Taken together the rise of parallel distributed processing and the end of Moore’s law has brought a renaissance in alternative views of computation. This talk is a journey through the rapidly changing area of non-standard computation: from GPU’s, tensor and neuromorphic processors to stochastic, temporal and quantum computation. The main aim of the talk is to describe the tremendous opportunities that currently exist for radical change in computational paradigms, and crucially for the open source community, in the delivery of these architectures.

Jonny Edwards is the CEO/CTO of Temporal Computing – the first business in the UK to focus on temporal computation methods. The work on temporal computing started in the Non-Standard Computation Group at York University, via several Unconventional Computing Conferences, and has since attracted VC and IUK funding to support long-term commercial exploitation.

It’s the people, stupid! (But the people aren’t stupid) — Hardware as an enabler to Heating as as Service

Why are clocks slowing down over western Europe like halving your heating bills at home?

Remember when at the start of the year a row in one corner of what used to be Yugoslavia caused clocks across Europe to slow down and eventually lose six minutes? Nothing technical was broken, and it’s a reminder that people issues can’t just be ‘fixed’ blindly with tech.

When a purely technical fix for energy efficiency is installed, for example a better boiler, savings tend to persist for many years, maybe for a decade if the tech lasts that long.

Solutions that may make as big a difference but rely on the people around it continuing to do something to assist, tend to have much shorter persistence. Maybe between one and four years.

We already have a smart radiator valve called “Radbot” that can knock 20–50% off your heating bills and pay for itself in a year. It requires very little input if any to do its job. But it won’t work if people open all their windows in winter and expect magic to happen. Yes, some people do.

We just finished an Innovate UK project “Heating as a Service – Lite”. We are more convinced than ever that while the technical and financial elements are probably easy to find solutions to, the social part, making things that work with real people for a long time, is intriguing!

Damon Hart-Davis created the OpenTRV project following his 2012 presentation to DECC’s smart heating workshop. He has freelanced in technology for over 30 years, delivering mission-critical products from design to production in the City for more than 20 of those, and has founded and been involved in several start-ups over that time with his creations seen on TV, the Web, and his pioneering Internet Service Provider helping crack open that market more than 25 years ago. A previous virtual/on-line credit-card company start-up that he co-founded as CTO, Ixaris, turns over ~GBP13m.

Bela, an embedded platform for ultra-low latency audio and sensor processing

Bela started off as a research project at Centre For Digital Music (Queen Mary University of London) and is now a commercial product, mainly aimed at makers, programmers and researchers that work with audio. The platform is based on a BeagleBone Black with a custom expansion cape and a dedicated software environment. The board runs Debian Linux with Xenomai as a real-time co-kernel. The combined use of Xenomai and the BeagleBone Black’s on-board PRU microcontroller allows to achieve sub-millisecond latency for audio and sensor processing, while node.js is used to provide a user-friendly web-based IDE. The project is entirely open source, hardware and software.

Giulio Moro is a PhD student in the Centre for Digital Music at Queen Mary University of London. A sound engineer by training, he is now researching in the field of performer-instrument interaction. He is one of the inventors and core developers of Bela.

Note that this talk was originally given at OSHUG #63 in London and is being repeated at OSHCamp as a refresher and to serve as an introduction for the workshop on the Sunday.

Compered by:

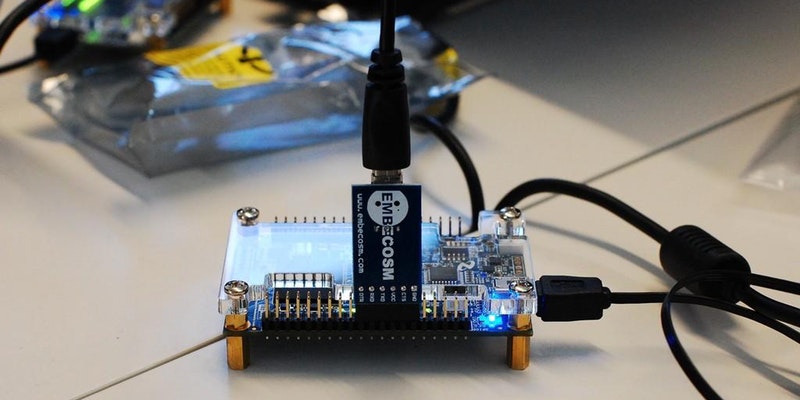

Dr Jeremy Bennett is founder and Chief Executive of Embecosm, a consultancy specializing in the development of open source compiler tool chains.

Sunday :: Workshops

Open-source RISC-V core quickstart

An introductory workshop for getting starting with simulating RISC-V cores using Verilator, which is an open-source tool for generating cycle-accurate models of hardware designs written in Verilog. Although this workshop focuses on simulation, the cores can in general be instantiated on FPGAs for use in real applications (and higher performance!)

The workshop will use two or three different RISC-V implementations (including Clifford Wolf’s PicoRV32 and Ariane from the PuLP platform). Loading and executing programs onto these bare metal systems through a testbench and also through a debugger (GDB) will be covered, along with some examples of interacting with the cores, and inspecting their state. Gathering accurate performance measurements is also possible, because the simulations are cycle-accurate.

The tutorial materials will provide enough implementation that it is possible to follow this workshop without having had prior experience of hardware design or Verilog specifically – however, some understanding of programming and the organisation of computer hardware will be required.

The workshop should be of interest to people with a background in software who would like to tinker with open-source processor core development, and people with a background in hardware who would like to tinker with software toolchains.

Participants should bring:

Run by: Dr Graham Markall

An introductory workshop to NetBSD on embedded platforms

An introductory workshop to NetBSD in the context of developing embedded platforms. NetBSD is a fully featured operating system with great agility that has been around for many many years. This workshop is intended to introduce some of the features which are available in the operating system as standard. We’ll explore how to go from obtaining the source code to building the operating system, cover features which simplify working with the system, how accessible it is without resorting to installing third party software or writing any C.

Topics we will cover:

- Cross compilation support with build.sh

- File tamper detection / execution prevention with Veriexec

- High-level access to subsystems e.g exploring GPIO via Lua

- Rapid development with Rumpkernel

Participants should bring:

- A laptop (Macos, Linux or Windows (windows 10 specifically))

- ARM board (BeagleBoneBlack preferably or a Pi and such)

- USB UART for serial access

Sevan Janiyan is founder of Venture 37, which provides system administration & consultancy services. As a fan of operating systems and computers with different CPU architectures, in his spare time he maintains builds of open source software on a variety of systems featuring PowerPC, SPARC and armv7l CPUs. He hopes to own a NeXTcube & OMRON LUNA-88K2 one day.

High Altitude Ballooning

An in-depth look at the help and advice available online, likely costs and technical issues for those wanting to build, fly and recover a HAB. If our project has some spares available, I’ll try and bring them along so people can see what’s being discussed.

If we’re lucky there may be a balloon launch somewhere in the world that we can follow during the session!

Participants should bring:

Run by: Tony Brookes

Machine Vision

A hands-on machine vision workshop – further details TBC.

Participants should bring:

Run by: Alan Wood

Soldering Workshop

A soldering workshop where novices get to assemble and program the Cuttlefish, Arduino-compatible, kit.

Chelsea Back is a trainee engineer and is working towards a degree in Electronic Engineering. She enjoys building microcontroller projects and teaching people how to solder, is a student member of the IET and a STEM Ambassador.

Build a Z80 based retro computer

A step-by-step build of a RC2014 Mini Z80 Retro Computer. Approx 2 hours should be enough time to assemble a computer running BASIC.

Participants will need to purchase a (heavily discounted) RC2014 Mini. Some soldering experience is assumed.

Participants should bring:

- Their laptop

- A soldering iron, wire cutters, FTDI cable and laptop if you have them

Run by: Spencer Owen

Bela: an embedded platform for ultra-low latency audio and sensor processing

This hands-on workshop introduces Bela, an embedded platform for ultra-low latency audio and sensor processing. Bela is useful for creating digital musical instruments and other interactive projects, which can be developed in C/C++, Pure Data (Pd) or Supercollider. The platform features an on-board browser-based IDE for getting started quickly. In this workshop we will guide participants through connecting sensors and accessing them from C++ or PureData and use them to control the generated sound. On Bela, sensor inputs are sampled at audio frequency and with high resolution (16bit), in order to allow for detailed, nuanced interactions. The hardware and software architecture allows sub-millisecond latency, allowing for expressive musical performances, as well as feedback control of physical systems.

Participants should bring:

Run by: Giulio Moro

Travel & Accommodation

For travel and accommodation details please see the OSHUG website.

Registration

To register vist: http://oshcamp2018.eventbrite.co.uk

Sponsored by:

The BCS OSSG and the OSHUG are hosting their next event on 23rd November 2017, 18:00 – 21:00 at

The BCS OSSG and the OSHUG are hosting their next event on 23rd November 2017, 18:00 – 21:00 at  Since the workshops held earlier this year, numerous changes have been made to the NetBSD operating system to ensure future workshops are easier for users and work smoother from the outset. This talk will cover some of the improvements made so far and what’s currently in the works. From wrestling with the u-boot firmware to new tools included in the os and much more.

Since the workshops held earlier this year, numerous changes have been made to the NetBSD operating system to ensure future workshops are easier for users and work smoother from the outset. This talk will cover some of the improvements made so far and what’s currently in the works. From wrestling with the u-boot firmware to new tools included in the os and much more. ChipHack is an occasional 2 day workshop introducing students and hobbyists to FPGA design. This year, ChipHack was sponsored by the BCS OSSG and Computer Conservation Society. To celebrate the 60th anniversary of the BCS, the workshop was extended by half a day and attempted to reimagine one of the earliest valve computers, EDSAC, designed by the BCS’ founding president, Prof Sir Maurice Wilkes.

ChipHack is an occasional 2 day workshop introducing students and hobbyists to FPGA design. This year, ChipHack was sponsored by the BCS OSSG and Computer Conservation Society. To celebrate the 60th anniversary of the BCS, the workshop was extended by half a day and attempted to reimagine one of the earliest valve computers, EDSAC, designed by the BCS’ founding president, Prof Sir Maurice Wilkes.