The fifty-fifth meeting will feature a series of shorter talks that explore past, planned and possible projects which use FPGAs.

FPGA Projects – What would I build and why would I want to

PLAs have been interesting ever since the 70s when digital logic often became complex, consuming unnecessary space and power. Back then the cost of PLA deployment was high and it has continued to be high until recently. Now that we have powerful, low cost development platforms and relatively cheap FPGAs the cost equation has shifted radically.

Paul Tanner is a consultant, developer and maker in wood, metal, plastic, electronics and software. His day job is IT-based business improvement for SMEs. By night he turns energy nut, creating tools to optimise energy use. Paul graduated in electronics and was responsible for hardware and software product development and customer services in several product and service start-ups, switching to consulting in 2000.

Using FPGAs to solve realtime problems

Microcontrollers a great platform to solve basic control problems in electronics, with simple motor drivers and sensors readily avaiable and easy to integrate. However, when the motor control becomes more complex with BLDC and FOC things get much more tricky. When you have to use multiple BLDC motors and more complex sensors with image processing the poor microcontroller quickly becomes to swamped to provide control in realtime. This is where adding FPGA technology makes a great deal of sense particularly in mutli-discipline projects like robotics where many sensors, motors and image processing will need to be managed and controlled concurrently. A robotics platform must therefore contain both concurrent hardware resources, algorithmic control through soft or hard cores along with communication protocols.

Alan Wood has been working with parallel distributed programming for several decades. His recent work includes smart grids, 3D printers, robotics, automation and biotec diagnostics. His current research is focused on machine learning, inference and image processing for embedded applications using FPGA and multi-cores. He is a long term advocate and moderator (aka Folknology) for xCORE and other opensource communities, as well as a founder of Surrey and Hampshire Makerspace and myStorm FPGA development boards.

FPGAs in the Cloud?

It is no secret that FPGA based computing machines are great at dealing with certain types of workloads that conventional CPU based machines can not efficiently handle. These machines, alongside their GPU and even custom ASIC based brethren, have been filling up racks in large data centres all over the globe helping speed up systems that have components of machine learning, complex analytics and even video processing.

This short talk will have a look at the state of FPGAs in the datacenter and discuss the recent developments around the availability of FPGA equipped computing nodes in commodity cloud providers.

Omer Kilic is an Embedded Systems Engineer who enjoys working with small connected computers of all shapes and sizes. He works at the various intersections of hardware and software engineering practices, product development and manufacturing.

Chip Hack 2017 & EDSAC Challenge

This talk will introduce and issue a call for participation for two events that are being hosted as part of the Wuthering Bytes technology festival, that will take place in Hebden Bridge in September, in the week following Open Source Hardware Camp 2017.

Chip Hack is a two day hands-on workshop that provides a gentle introduction to programming FPGAs and is aimed at novices with no prior experience of Hardware Description Languages (HDLs) or FPGAs. This will be followed immediately by a challenge event, during which a small team of experts will work to extend a basic functional FPGA model of EDSAC — the pioneering computer designed and constructed at Cambridge University, and which was operational by 1949.

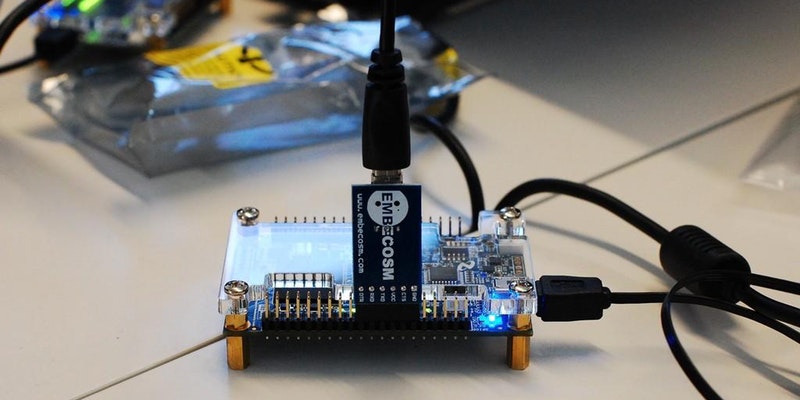

Dr Jeremy Bennett is founder and Chief Executive of Embecosm, a consultancy implementing open source compilers and chip simulators for major corporations around the world. He is a author of the standard textbook “Introduction to Compiling Techniques” (McGraw-Hill 1990, 1995, 2003). Contact him at: jeremy.bennett@embecosm.com.

7th February update: 2 extra talks!

Deploying your FPGA toolchain consistently regardless of your development environment

With an open source tool chain for an open hardware fpga, we’re free to work in the environment of our choice. What may differ between platforms is how we put the components together, from requiring software dependences to administrative commands needed to be executed in order to build to software successfully.

pkgsrc is a cross platform packaging system which allows you to deploy open source software consistently, regardless of the environment it is operating on. This means should you desire to install the icestorm tool chain, the steps required to build or install packages is the same whether you’re running a flavour of Linux, Mac OS or Windows.

This lightning talk will introduce pkgsrc and how you can get started quickly with icestorm and other tools to help with your hardware project.

Sevan Janiyan is founder of Venture 37, which provides system administration & consultancy services. As a fan of operating systems and computers with different CPU architectures, in his spare time he maintains builds of open source software on a variety of systems featuring PowerPC, SPARC and armv7l CPUs. He hopes to own a NeXTcube & OMRON LUNA-88K2 one day.

Multicore Made Simple – Conducting a Chorus of Cores on an FPGA

FPGA technology makes it simple to build a multicore CPU, by instantiating multiple copies of a soft processor design on a single chip. The challenge is to connect and coordinate the cores into a resource which is useful for application programming. While traditional multicore processors include shared memory, shared buses and/or general communications networks, all of these are costly in hardware resources and complexity, and subtle details of synchronization and cache coherency can make programming difficult and risky. Building our own system on an FPGA, we can choose a minimalist “shared nothing”

architecture, with only local memories and simple synchronous point to point communications links in a topology tailored to the application. As an example of this approach, I’ll demonstrate a 40 voice (plus

conductor) polyphonic digital audio synthesizer, running on an array of

41 Nios2 cores on an Altera Cyclone II.

Dr Richard Miller has had a long career in the borderlands between hardware and software, in academia and industry and now as an independent consultant. Particular interests have been operating systems portability (starting in 1977 with the world’s first UNIX port, from

PDP/11 to Interdata 7/32 at the University of Wollongong; and most recently porting the Plan 9 OS to the Raspberry Pi); programming language implementations in constrained environments (e.g. a LOGO interpreter on a 48KB Apple II; and a JavaCard JVM and runtime library on a smartcard with a 8KB of RAM and 1MB of flash); parallel computing infrastructure (on hardware ranging from Transputers to the Cray T3D); and embedded systems firmware (e.g. a complete Bluetooth stack for a range of prototype phones and tablets). Current work in progress includes building a communications network on an FPGA, for a microcluster of Raspberry Pi Zeroes.

Note: Please aim to arrive by 18:15 as the event will start at 18:30 prompt.

On the 20 April 2017, 17:30 – 20:00 at

On the 20 April 2017, 17:30 – 20:00 at  Since graduating from the Department of Computing at Imperial College, London in the early 1990s, Nick Stylianou has worked in the IT industry as a CAD/CAM software developer, UNIX Systems Administrator & Enterprise Architect, and a Text and Data Mining Analyst. He now works independently, specialising in Research & Development in Computational Musicology, with current projects including a forthcoming music theory reference eBook and interactive music theory and analysis software.

Since graduating from the Department of Computing at Imperial College, London in the early 1990s, Nick Stylianou has worked in the IT industry as a CAD/CAM software developer, UNIX Systems Administrator & Enterprise Architect, and a Text and Data Mining Analyst. He now works independently, specialising in Research & Development in Computational Musicology, with current projects including a forthcoming music theory reference eBook and interactive music theory and analysis software. The heart of the day is to provide a practical ‘hands-on’ afternoon session using the LimeSDR with the

The heart of the day is to provide a practical ‘hands-on’ afternoon session using the LimeSDR with the