25 Copthall Ave

London EC2R 7BP

This is our quarterly meetup for the London open source community, focusing on RISC-V, hosted by the BCS Open Source Specialist Group and the UK Open Source Hardware User Group. These meetings provide an opportunity to share the latest ideas around open source in the RISC-V ecosystem, combined with plenty of time for networking. Please discuss, give feedback and suggest future topics on the London Open Source Meetup group event page.

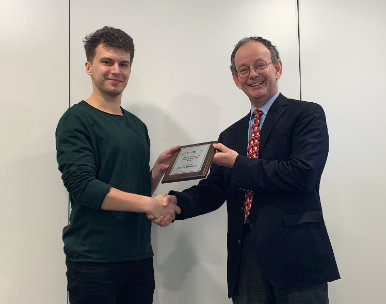

At this evening meeting we have three talks on the MaxineVM on RISC-V, Embench on RISC-V and open source licensing with RISC-V. One of our speakers, Florin-Gabriel Blanaru, was winner of the inaugural RISC-V Student of the Year competition. At this meeting he will be presented with his award and then speak about his work. The presentation will be made by Mary Bennett, Chair of the RISC-V Foundation University Outreach committee.

Note. This meeting is at the new BCS London offices, 25 Copthall Ave, EC2R 7BP.

The talks will be live streamed and available on afterwards on the BCS Open Source Specialist Group YouTube channel.

Tea/coffee will be served from 6:00pm, with talks starting at 6:30pm. Each talk will last around 30 minutes and include plenty of time for questions, after which there will be opportunity to network both in the BCS and later at the Globe pub round the corner.

We shall be livestreaming and recording the talks for later posting on YouTube via GoToWebinar. Registration details to follow shortly. Please register at:

attendee.gotowebinar.com/register/1776873866939508491

After registering, you will receive a confirmation email containing information about joining the webinar.

Free and Open Source Licensing and RISC-V

Andrew Katz, @andrewjskatz

Andrew will present the results of his research on the current state of open core licensing, and his thoughts on the direction of travel for licensing in the future. He will also give an update on the CERN Open Hardware licence, and how V2 has been redrafted with the concerns of developers of ASICs and FPGAs.

Andrew Katz, a partner at Moorcrofts LLP, is one of the UK’s leading free and open-source lawyers. He drafted the widely-used solderpad Open Hardware Licence and is on the core legal team for drafting the CERN Open Hardware licence. Andrew is a Fellow of the Free Software Foundation Europe and the Open Forum Academy, and for 7 years held the post of visiting lecturer at Queen Mary, University of London. He is a visiting researcher at the University of Skövde, Sweden where he has co-authored papers whose findings have been adopted into Swedish government policy.

Andrew qualified as a barrister and was called to the bar (Inner Temple) in 1991, and has now re-qualified and practises as a solicitor in England and Wales. He is also an Irish solicitor (non-practising).

MaxineVM on RISC-V

Florin-Gabriel Blanaru

In this talk we will talk about MaxineVM’s, a metacircular research VM, in relationship to the RISC-V architecture.

A short overview of the current JVM ecosystem on the RISC-V architecture will be presented first.

Next we will proceed with a high level view of MaxineVM along with a description of the work that had to be accomplished for the RISC-V port.

A comparison of MaxineVM’s performance against OpenJDK Zero will follow and we will conclude with a description of our current and future research on safe code modification on architectures without SMC hardware support.

Florin-Gabriel Blanaru is currently a research software engineer at the University of Manchester. During his bachelor’s degree at the University of Manchester, he successfully ported MaxineVM to the RISC-V architecture. He is interested in all the abstraction layers between the hardware and the programming languages, including computer architecture, operating systems and managed runtime systems. Florin is the inaugural winner of the RISC-V Student of the Year award.

Evaluating RISC-V using the Embench™ 0.5 Benchmark Suite

Jeremy Bennett, @jeremypbennett, @embenchorg

Dhrystone and Coremark have been the defacto standard microcontroller benchmark suites for the last thirty years, but these benchmarks no longer reflect the needs of modern embedded systems. Embench™ was explicitly designed to meet the requirements of modern connected embedded systems. The benchmarks are free, relevant, portable, and well implemented.

In this talk we will present the results of benchmarking RISC-V for various IoT class architectures using Embench. We shall look at what this tells us about the impact of architecture, compilers and libraries on how a system performs, both in terms of code size and code speed. The aim is not to show which architecture, library or compiler is best, but to gain insight allowing all architectures to be improved.

Dr Jeremy Bennett is Chief Executive of Embecosm, a company based in the UK and Germany providing services developing open source compilers, operating systems and chip models. He is Vice-Chair of the Embench Task Group, and has been one of the main developers of the benchmark infrastructure. Jeremy is a Fellow of the BCS where he serves as Chair of the Open Source Specialist Group.